|

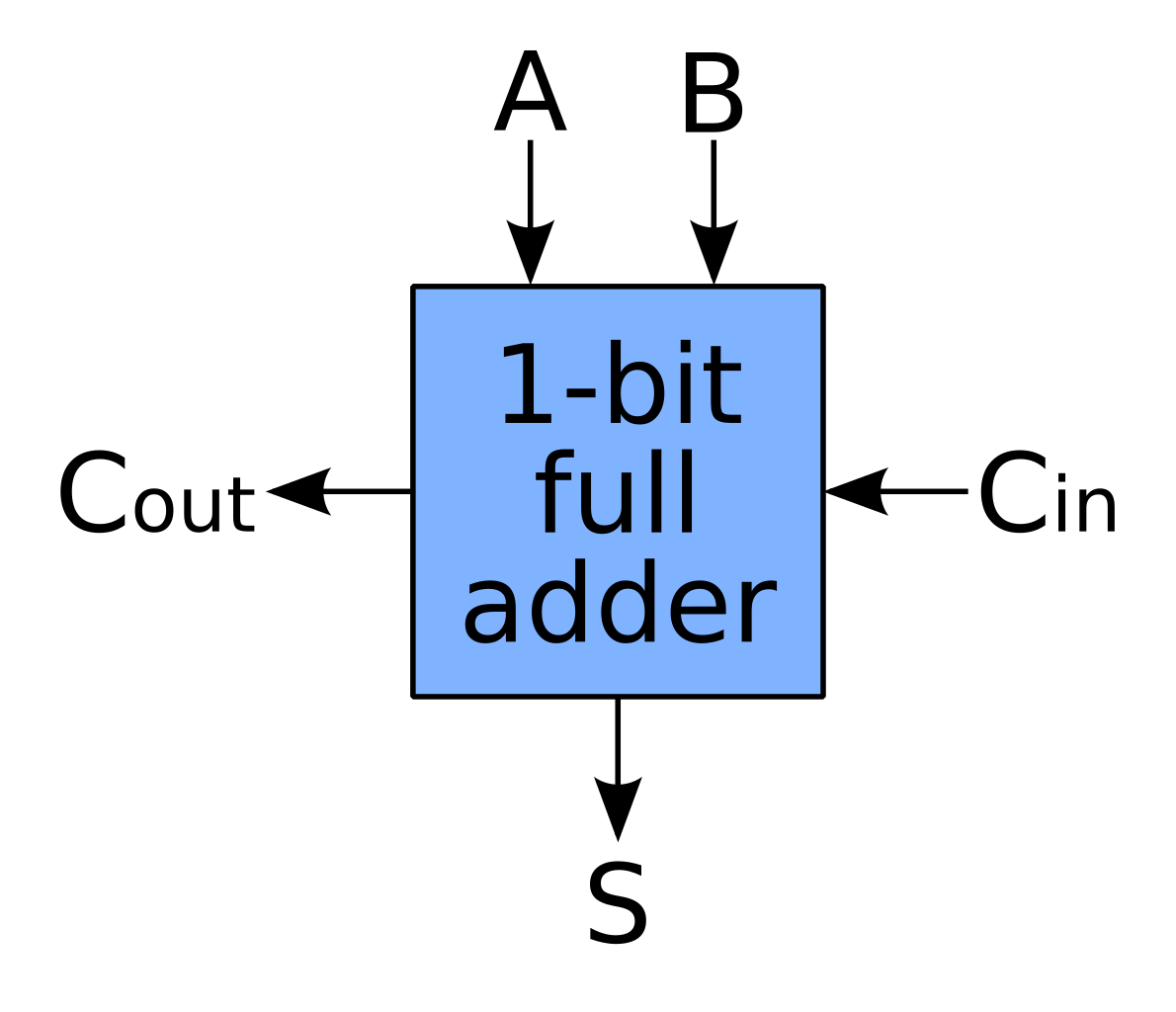

CS3. 20- Computer Organization and Architecture. Introduction. An adder or summer is a digital circuit that performs addition of numbers. This tutorial will describe the VHDL code for a full adder using two half adder. Full Adder. In modern computers adders reside in the arithmetic logic unit (ALU) where other operations are performed. A full adder is a logical circuit that performs an addition operation on three one- bit binary numbers(A, B and Cin). The full adder produces a sum and a carry.

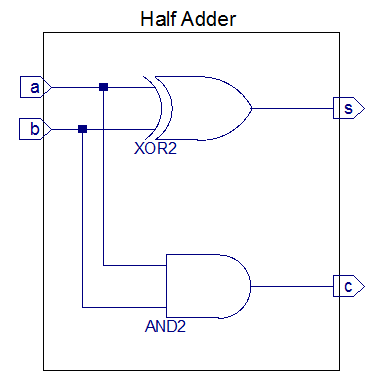

This VHDL program is a structural description of the interactive Half-Adder on teahlab.com. The program shows every gate in the circuit and the interconnections between the gates.The circuit under verification, here the Half Adder, is imported into the test bench. Electrofriends.com Source Codes Digital Electronincs Verilog HDL Verilog HDL Program for HALF ADDER. With the addition of an OR gate to combine their carry outputs, two half adders can be combined to make a full adder. Half Adder 1 2 3 4 5 6 module ha ();. Debashish Mohapatra's Information Portal for the persons in need of some introductory coursework/Examples to various Electronic/Microcontroller or Technical Projects. Home VLSI Design VHDL Codes Tanner Tools Lab Manuals TSpice Codes E-Learning. FULL ADDER AIM: To design, implement and analyze all the three models for full adder. Design: First, VHDL code for half adder was written and block was generated. Half adder block as component and basic gates, code for full adder is written.

Subject: EESB423 VLSI Semester 3, 2011/2012 2 bit adder using VHDL coding. Software: Quartus II & ModelSim. Introduction The saying goes that if you can count, you can control. Addition is a fundamental. One way of implementing a full adder is to utilizes two half adders in its implementation. The full adder is the basic unit of additionhere A halfA. This VHDL program is a structural description of the interactive Full-Adder on teahlab.com. The program shows every gate in the circuit and the interconnections between the gates.The circuit under verification, here the Full Adder, is imported into the test bench. FULL ADDER AIM: To design, implement and analyze all the three models for full adder. Design: First, VHDL code for half adder was written and block was generated. These include the EDA Lab Programs using VHDL: Adders (HA, FA, RCA, CLA), Subtractors.

Below is the truth table of a full adder. From the previous example the entity declaration of half adder was defined as follows. On the other hand Cin and Y0 is the input of second half adder(HA1) and output is Sum and Z1(carry out). Carry of HA0 and HA1 is the input of a or- gate and the result is the carry of the full adder. Simulator waveform of full adder is given below. Create a folder and download the source file to that folder. Now open modelsim and create a new project from File- > New- > Project. Right click on the source pane and select . Create a new . do file from File- > New- > Source- > Do. Copy the following code and save the file as . Compile it(Compile- > Compile All)6. Start Simulation(Simulate- > Start Simulation)7. Now click on wave tab and analyze the output. The output should be similar to the above image.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. Archives

December 2016

Categories |

RSS Feed

RSS Feed